主存储器的基本组成

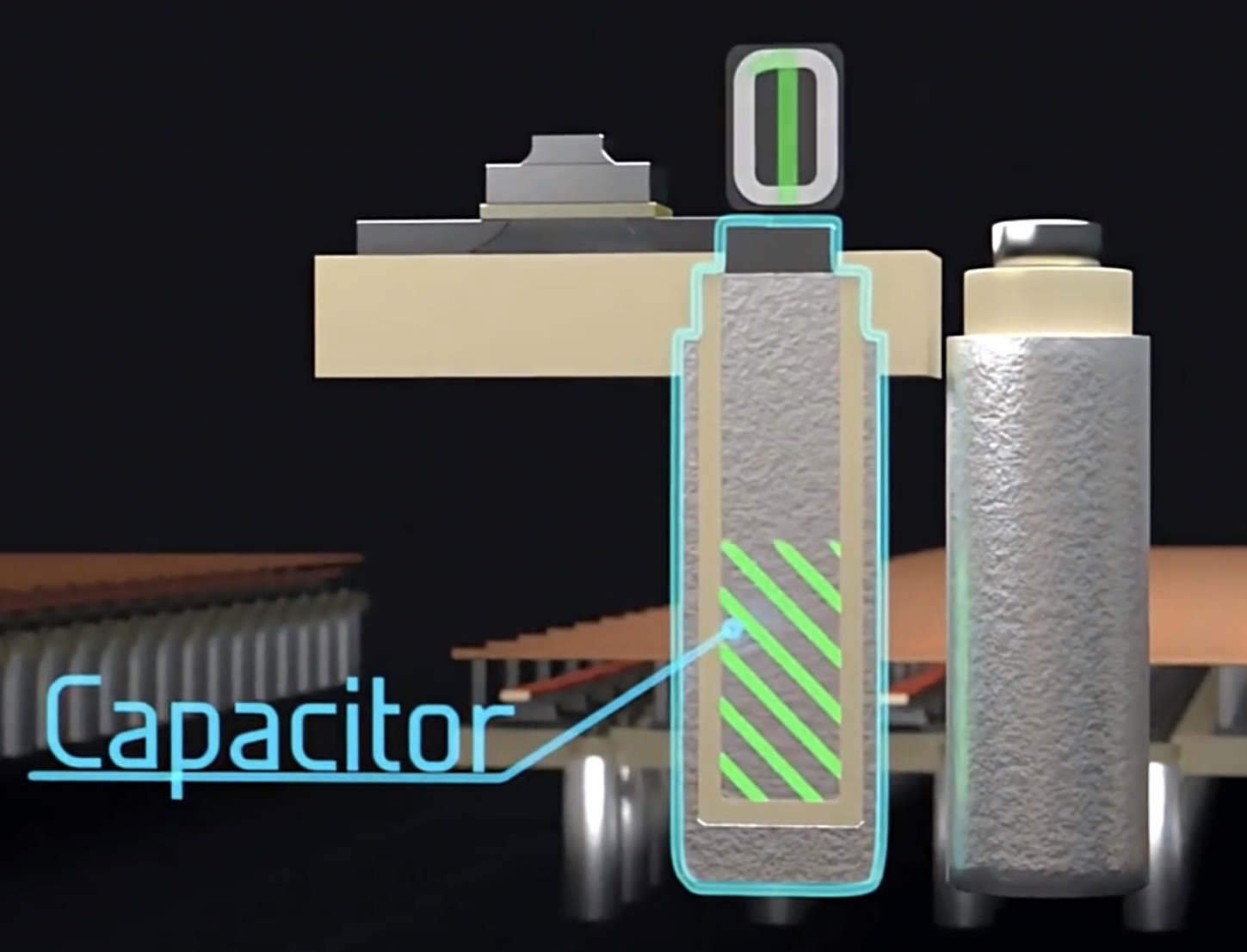

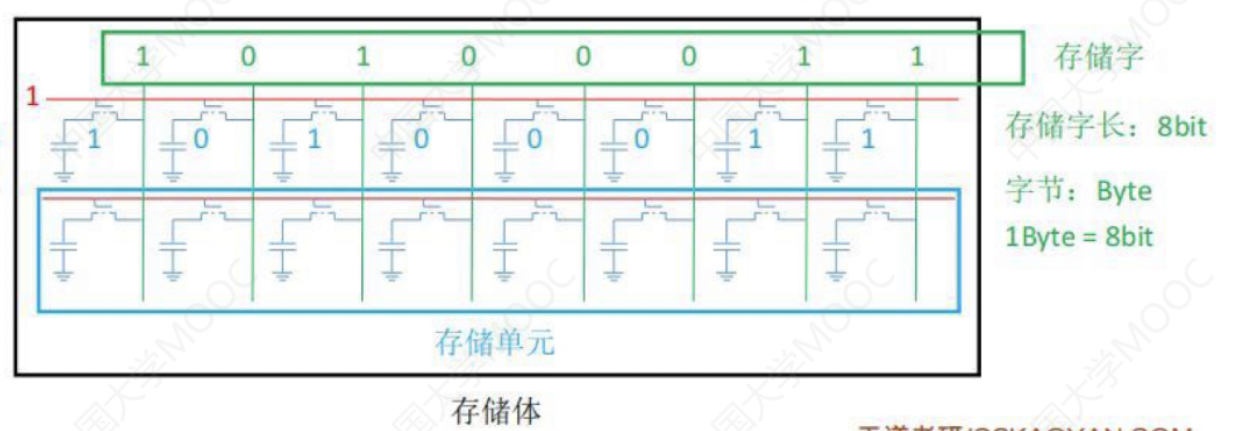

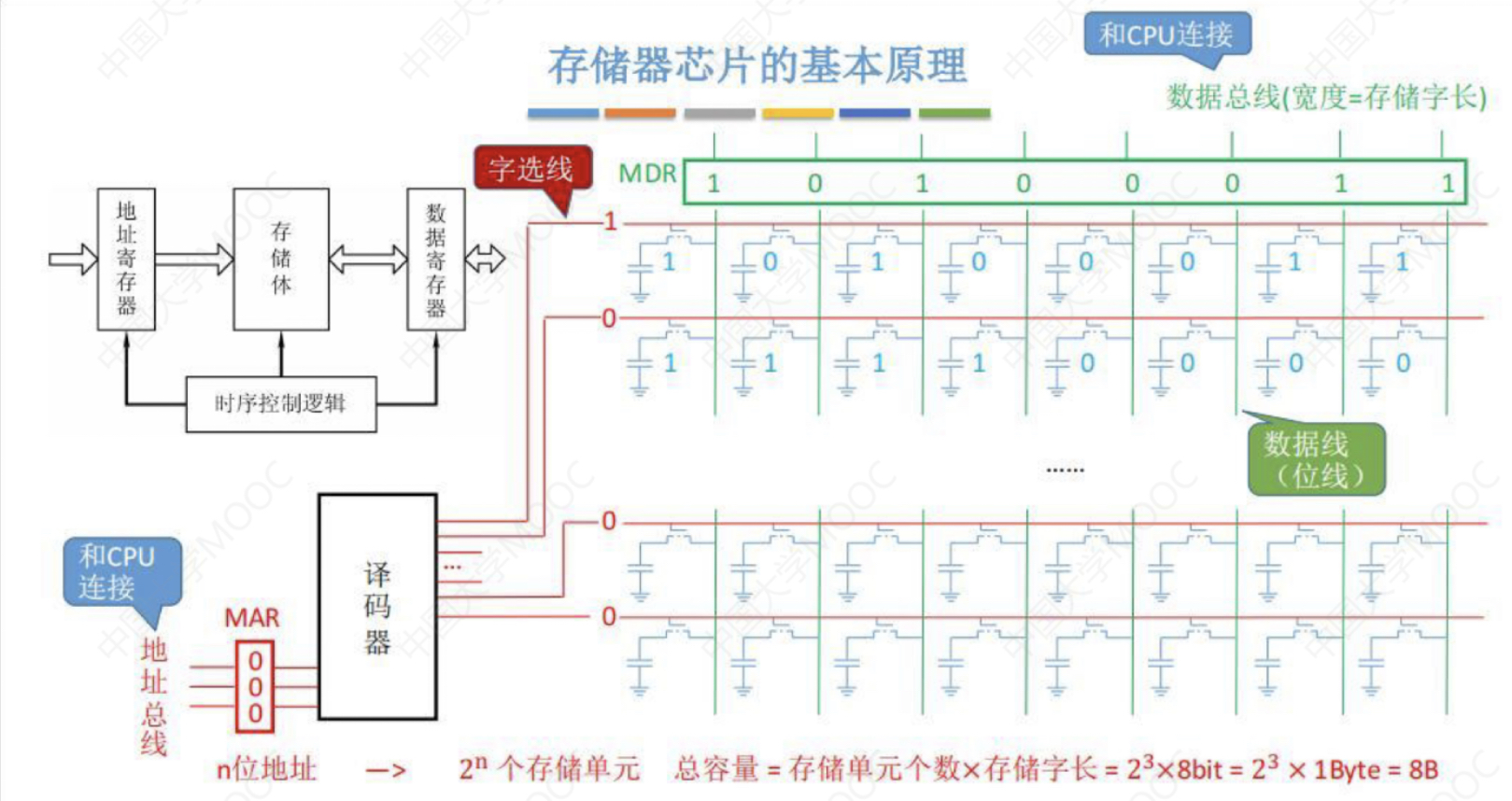

- 存储器最小的存储结构为存储元,0和1存储在电容中,通过MOS管的通断点控制电容充放电(存0或1)

8个存储元(存储字长=8)排在一排就构成了一个存储单元,接在一根数据总线上(总线宽度=存储字长=8),若干个存储单元放一块就成了存储体(硬盘上的一个黑块块)

总容量 = 存储字数 * 存储字长

数据线的宽度 = MDR的宽度 = 存储字长

地址线的宽度 = MAR的宽度 = 存储字数 = 2存储单元行数

- 36位地址线的宽度为236

- 36位地址线的宽度为236

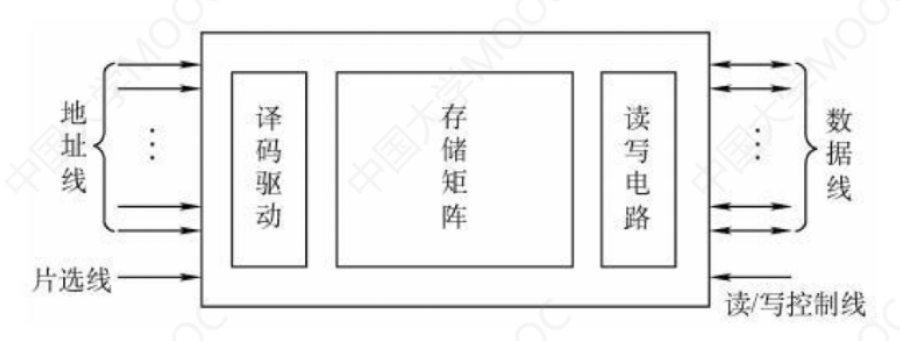

存储体+IO/读写电路+地址译码器+读写控制信号 = 主存储器

- 读RD/写WR控制线:决定芯片是进行读还是写操作

- 片选线CS:确定那个存储芯片被选中。可用于容量扩充

- 引脚最低数目 = 片选线(1条) + 控制线(RD+WR = 2条) + 数据线 + 地址线

寻址方式

题目没有明确指定按字编址,默认就是按字节编址(一字节8位)

- 64位计算机中,64位(bit) = 8字节(byte) = 1字(word)

- 32位计算机中,32位(bit) = 4字节(byte) = 1字(word)

存放一个机器字的存储单元,通常称为字存储单元,相应的单元地址叫字地址

存放一个字节的存储单元,称为字节存储单元,相应的地址称为字节地址

如果计算机中可编程的最小单位是字存储单元,则该计算机称为按字寻址的计算机

如果计算机中可编程的最小单位是字节,则该计算机称为按字节寻址的计算机

一个机器字可以包含数个字节,所以一个存储单元也可以包含数个能够单独编制的字节地址

- 例:一个16位二进制的字存储单元可以存放两个字节,可以按字编址,也可以按字节编址。当用字节编址时,16位存储单元占用两个字节地址

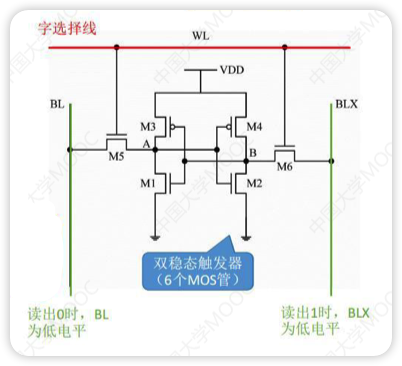

SRAM芯片和DRAM芯片

| SRAM(Static Random Access Memory) | DRAM(Dynamic Random Access Memory) | |

|---|---|---|

| 主要用途 | Cache | 主机内存 |

| 存储信息(核心区别) | 触发器,双稳态电路 | 栅极电容(前面的存储元) |

| 破坏性读出(读出后需要重写) | ❌ | ⭕️ |

| 需要刷新 | ❌ | ⭕️ |

| 送行列地址 | 同时 | 分两次送(地址线复用技术) |

| 运行速度 | 快(读出后不用重写) | 慢 |

| 集成度(容易混) | 低 | 高 |

| 存储成本(对比两种存储元结构就知道) | 高 | 低 |

| 功耗(发热量) | 高 | 低 |

| 易失/非易失性存储器 | 易失(断电后信息消失,电脑一关机就没了) | 易失(断电后信息消失,电脑一关机就没了) |

双稳态电路:

破坏性读出:前面的存储元结构,读出数据时,如果是1,电容中的电荷会流失,导致原有的信息被破坏,读出后需要有重写操作(再生)

DRAM的刷新

DRAM电容的电荷维持时间短,即使电源不断电信息(电荷)也会自动消失。因此每隔一段时间必须刷新,一般取2ms(刷新周期/再生周期)

DRAM的刷新是以行为为单位

一次完整的刷新过程只需要占用一个存储周期

刷新时间=存取周期

- 刷新其实还是往电容里充放电,与存取一样,所以时间相同

- 存取周期如果是0.5μs

存取周期>真正用于存取的时间

- 存取周期内,存取操作结束后仍然需要一些时间来改变状态

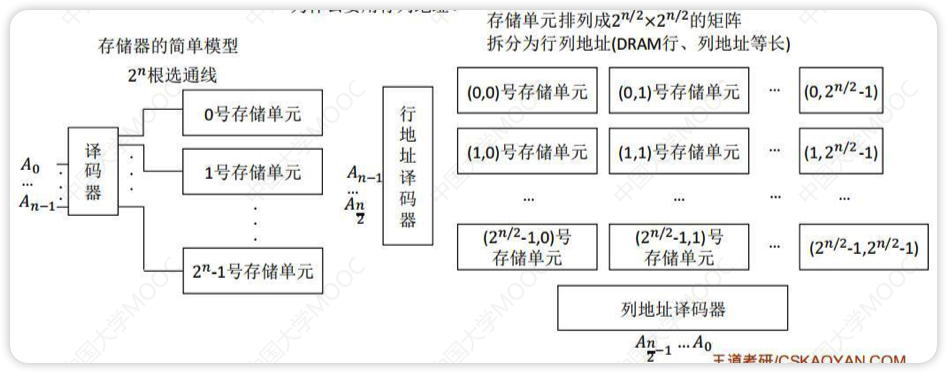

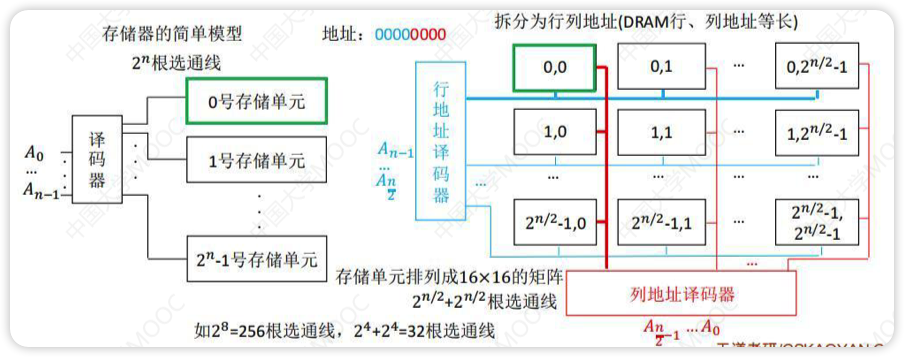

行列地址

DRAM刷新

以行为单位,每次读出来一行然后重新写入,占用一个存取周期

假设DRAM内部结构排成128 * 128的形式,存取周期0.5μs,2ms共2ms/0.5μs=4000个周期

由存储器独立完成,不需要CPU控制

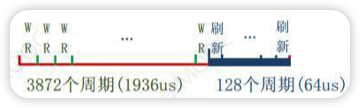

集中刷新

- 2ms内集中安排时间全部刷新

- 系统的存取周期不变,还是0.5μs

- 在2ms中的最后一段时间内专门进行刷新,这段时间被称为“死区”

- 全部刷新需要128行*0.5μs/行 = 64μs,即死区占用64μs

分散刷新

- 每次读写完就刷新一行

- 系统的存取周期变为1μs,前0.5μs正常读写,后0.5μs用于刷新

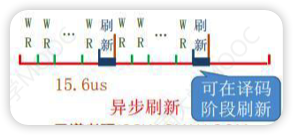

异步刷新

- 一共需要128次刷新,均匀分布到2ms中

- 即每隔2ms/128=15.6μs刷新一次,每15.6μs内有0.5μs的“死时间”

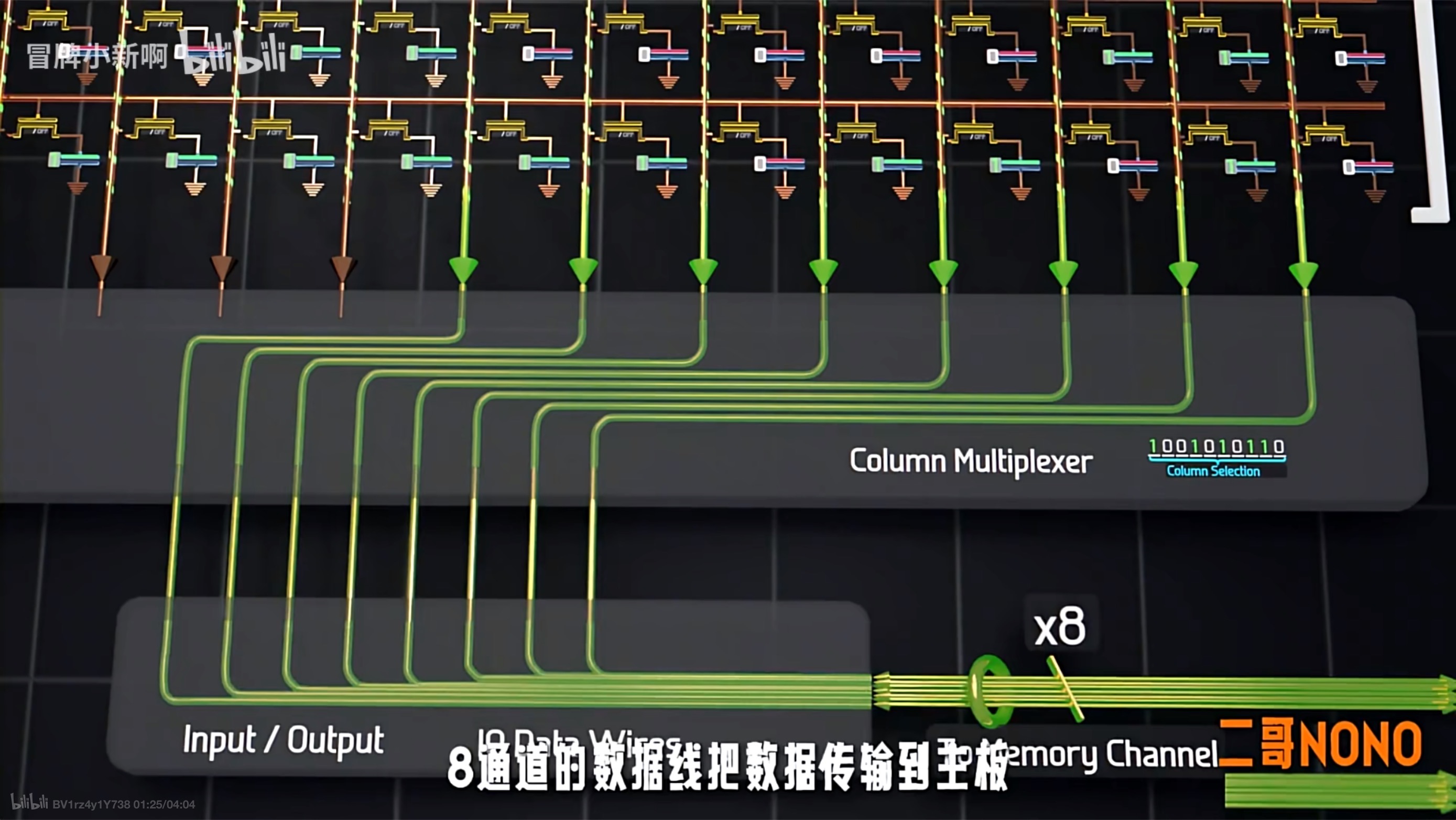

地址复用技术

- 由于DRAN芯片容量大,地址位数多,为了减少地址引脚线,采用地址复用技术

- DRAM因为分两次发送,长度相同,因此地址线可以复用,线数减少了一半

- 引脚数 = 地址线减半 + 数据线不变 + 行通选(1条) + 列通选(1条) + 读写控制线(2条)

- 片选线用行通选线替代

- DRAM采用地址复用技术,SRAM不采用

只读存储器

特点

- 结构简单,位密度比可读写存储器高

- 具有非易失性,可靠性高

- 随机存取

类型

掩模式只读存储器(MROM, Mask Read-Only Memory)

- 内容在生产过程中写入

- 可靠性高,集成度高,价格便宜,灵活性差

一次可编程只读存储器(PROM, Programmable Read-Only Memory)

- 用于用户实现一次性编程

可擦除可编程只读存储器(EPROM, Mask Read-Only Memory)

- 用于用户实现多次性编程

- 可多次改写,但次数有限,写入时间过长

Flash存储器

- 既可在不加电的情况下长期保存信息,又能在线进行快速擦除和重写

- 价格便宜,集成度高,电可擦除重写且擦除重写速度快

- 写的速度一般比读更慢,因为写入前需要先擦除

固态硬盘 SSD

- SSD即闪存,是一种非易失性存储器,采用随机访问方式

- 可长期保存信息,快速擦除和重写,相比传统硬盘也有读写快、低功耗的特性,但价格较高

双端口RAM

存储器左右都有独立的端口,分别具有两组独立的地址线、数据线和读写控制线

- 作用:优化多核CPU访问同一根内存条的速度

两个端口对同一主存操作的4种情况

两个端口不同时对同一地址单元存取数据

两个端口同时对同一地址单元读出数据

两个端口同时对同一地址单元写入数据

- 写入错误

两个端口同时对同一地址单元,一个写入数据,另一个读出数据

- 读出错误

解决方法:置“忙”信号为0,由判断逻辑决定暂时关闭一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间短后再访问

多模块存储器

多模块存储器是一种空间并行技术,利用多个结构完全相同的存储模块的并行工作来提高存储器的吞吐率

单体并行存储器

存储器中只有一个存储体,每个存储单元存储m个字,总线宽也为m个字,地址必须顺序排列并处于同一存储单元

- 在一个存取周期内,从同一个地址取出m条指令,然后将指令送到CPU

- 缺点:指令和数据在主存内必须是连续存放的,一旦遇到转移指令,或操作数不能连续存放,这种方法的效果就不明显

多行并行存储器

由多体模块组成,每块都有相同容量和读取速度,各模块都有独立的读写控制电路、MAR和MDR,既能并行工作也能交叉工作

| 高位交叉编址(顺序方式)(竖) | 低位交叉编址(交叉方式)(横) | |

|---|---|---|

| 定义 | 【特点】先在一个模块内访问,等访问完再访问下一个 【编号】高位地址表示体号(模块号),低位地址表示体内地址 【优点】 某个模块进行存取时,其他模块不工作 某一模块出现故障时,其他模块可以正常工作 通过增添模块来扩充存储器容量比较方便 【缺点】各模块串行工作,存储器的带宽受到了限制,并不能提高吞吐量 | 【特点】 连续地址分布在不同模块内,同一模块内的地址是不连续的 低位交叉编址是交叉存放的,满足程序的局部性原理 【编号】高位地址表示体内地址,低位地址表示体号(模块号) 【优点】对连续字的成块传送可实现多模块并行存取,提高了存储器带宽 【计算】 1. 每个模块按"模m"交叉编址,模块号=单元地址 % m 2.设模块字长等于数据总线宽度,模块存取一个字的存取周期为T,总线传输周期为r,则存储器交叉模块的数目最小为m=T/r 3.每隔r时间延迟后启动下一模块,当数目不小于m时,就可以保证T时间之后再启动该模块,流水线就不会断 4.取m个字的时间为T+(m-1)r,顺序方式时间为mT 5.判断发送访问冲突的规则:给定的访存地址在相邻的四次访问中出现在同一个存储模块中(m=4时) |

| 示意图 |  |  |

| 计算带宽 |  | 模块数=m,存储周期T,字长W,数据总线宽度W,总线传输周期r,连续存取n个字 顺序t = mT 交叉t = T + (m-1)r |

| 流水线 | 画图数数(参考错题集第3个) |

错题集

答案与解析:

答案: B

解析:

分散刷新是把死时间分散到每个存取周期后边,相当于把存取周期变长了,也就没有了死时间

答案与解析:

答案: B

解析:

低位交叉存储器采用流水线技术,可在一个存取周期内连续访问4个模块

32位 * 4 = 128位

答案与解析:

答案: C

解析:

答案与解析:

答案: D

解析:

用4个16Kx8的存储芯片可以组成64Kx8的存储器

交叉编址低位存放片选地址,片选地址一共4个所以最后两位是片选地址

最后两位是11,所以是3号存储芯片,即0003H

答案与解析:

答案: A

解析:

8位 = 8根数据线,4M = 222 => 22根地址线

DRAM采用地址复用,地址线减半(本题未考虑行列片选线),所以引脚总数为8 + 22/2 = 19根

答案与解析:

答案: B

解析:

DRAM需要周期性刷新

答案与解析:

答案: C

解析:

double数据占64位(8B) 一个芯片是8位,所以需要读64/8=8个芯片